# 100 Gbps data acquisition system prototyping

#### **Progress and Challenges**

Alberto Dassatti Jan 23, 2024

Who we are

## **Hes**·so

# HE<sup>v</sup> IG

**REDS** Institute Reconfigurable and Embedded Digital Systems

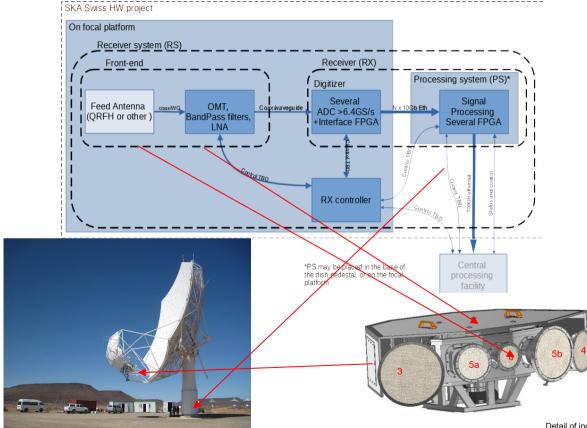

## **System View**

#### **System View**

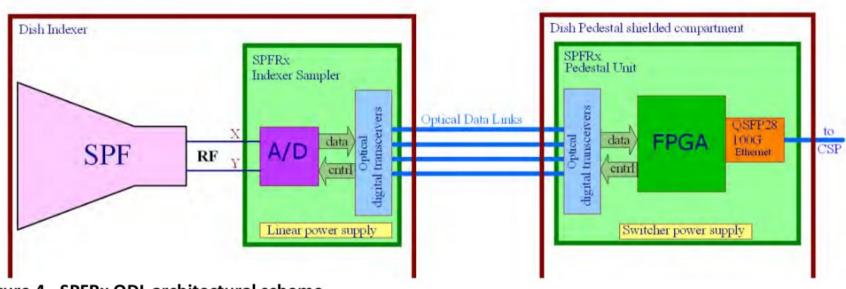

Figure 4 - SPFRx ODL architectural scheme

**RXPU**

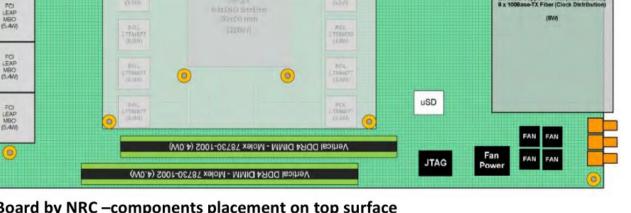

Figure 88 - TALON-DX Board by NRC –components placement on top surface

0

Vertical DDR4 DIMM - Molex 78730-1002 (4.0W)

0

Heat Sink

0

FOI

MBO (5.4/1)

FOI MBO (5.41)

Molex 100014-1240

(3.0W)

Airflow

Micro USB-8 0

OSFP28 Cage

Molex 100014-1240

(3.0W)

Main

Power

1x8 SFP4 Cages TE 2204409-1 2 x 1GbE Copper or Fiber (M&C Ethernet)

#### **EBB Specs and Interfaces**

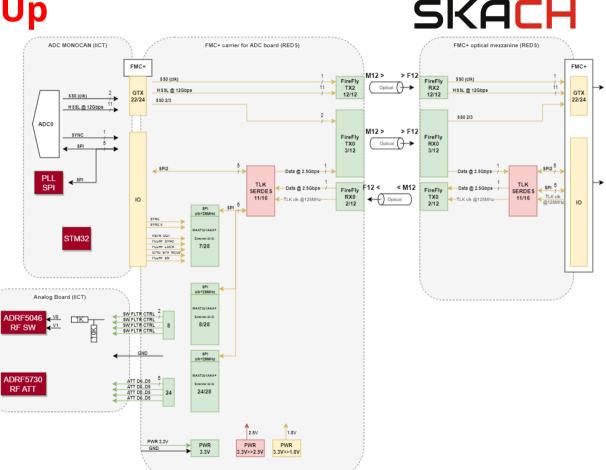

From ADCs to 100Gb/s Ethernet:

- 2 ADCs 12.5 Gs/s Data format: 10 b/s FMC connector

- Optical fiber isolation between ADCs and FPGA processing

- Talon compatible (future integration?) as much as possible

## **Prototyping Set-Up**

2 Custom made Boards to interface the ADC board with the FPGA board via optical fibers.

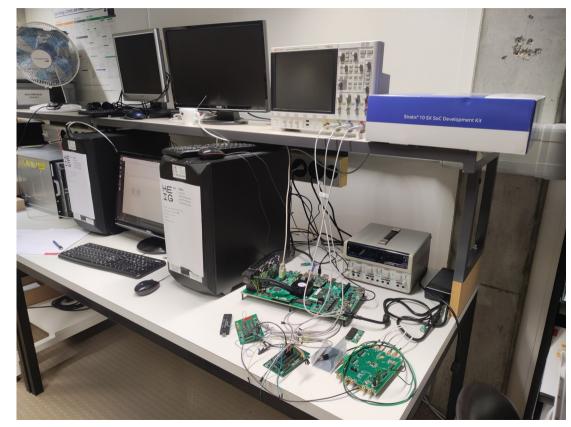

#### **Prototyping Set-Up**

#### **Prototyping Set-Up**

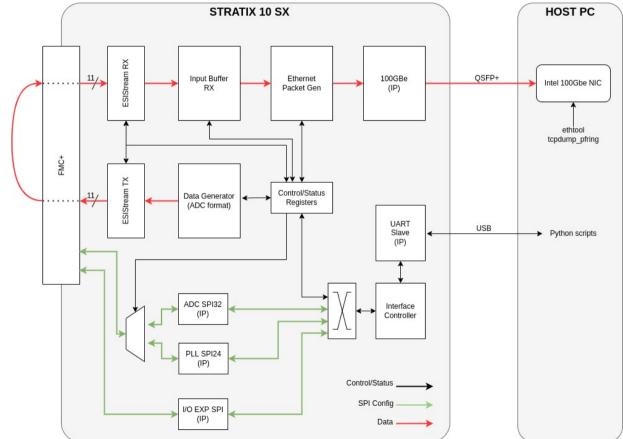

#### Hardware test design

## **Connecting a 100Gb/s cable is...**

...not enough

| Ethernet                                | 10M     | 100M (Fast) | 1G (Gigabit)  | 10G     | 100G     |                                             |

|-----------------------------------------|---------|-------------|---------------|---------|----------|---------------------------------------------|

| Time per bit                            | 100 ns  | 10 ns       | 1 ns          | 0.1 ns  | 0.01 ns  | DDR latency<br>~100 ns<br>Syscall<br>~10 us |

| Time for a MTU size<br>frame 1500 bytes | 1500 us | 150 us      | 15 us         | 1.5 us  | 150 ns   |                                             |

| Time for a 64 byte<br>packet            | 64 us   | 6.4 us      | 640 ns        | 64 ns   | 6.4 ns   |                                             |

| Packets per second                      | ~10 K   | ~100 K      | ~1 M          | ~10 M   | ~100 M   |                                             |

| Packets per 10 us                       |         | 2 (small)   | 20<br>(small) | 6 (MTU) | 60 (MTU) |                                             |

Christopher Lameter, Berlin 2016

## Linux software stack

Worst possible situation, single very fast transmission:

- No Flow steering (Intel at least)

- No NIC multi-queue support

- No per-Core processing

- No BPF help

- NO XDP help

PF\_RING™

High-speed packet capture, filtering and analysis.

# /usr/local/sbin/tcpdump\_pfring --version tcpdump\_pfring version 4.9.3 libpcap version 1.9.1 (with TPACKET\_V3)

#### Measurements

Max data rate achieved ~97 Gbps (with syntetic data generated by the FPGA)

ADC interface:

#### 2 ADCs X 12.5 Gbps X 4 bits/sample = 100 Gbps

->

All the stream can not be transmitted on 100GbE.

Proposed solution is to reduce the lane rate to 11.5 Gbps.

Data rate achieved: Stream of ADC A or B: 46.3 Gbps Stream of ADC A and B : 92.7 Gbps

#### What's next

Optical interface Boards:

- Routing to be completed

- Design Review

- Production:

- Optical components lead time 7ws

- Board production and assembly 5ws

- Test

#### PC Software:

- Acquisition Control

- Full system test

FPGA Design:

- Double ADC test on-going

- ADC Board integration test

- Optical boards test

- Full system test