SKA-Low site in Western Australia SKA Precursor telescope - MWA

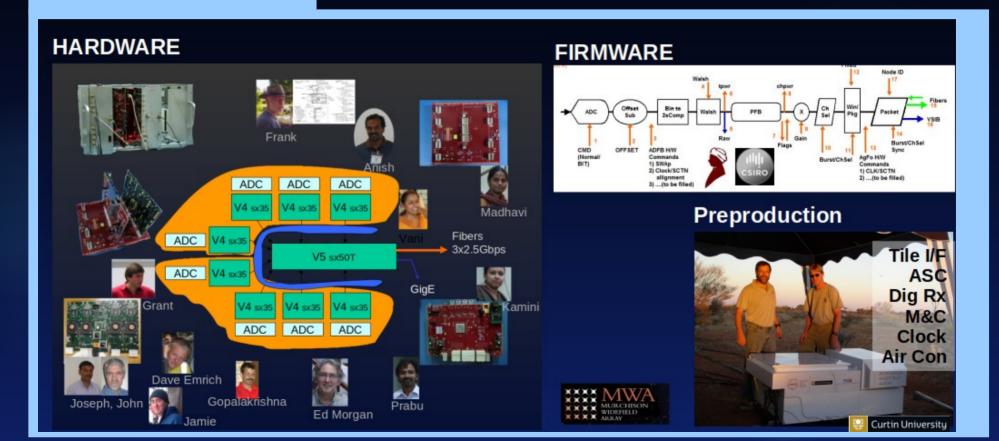

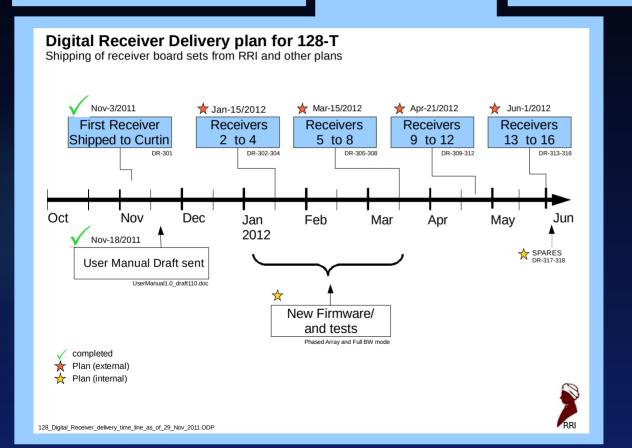

128 Antenna Digital receivers-2012 Design / HW / FW / Commissioning

**Project Meetings**

- Industry and academia involvement: Design Assembly Validation

- **5** Student Participation

- **6** Relevance & beyond

- **7** Agile

We acknowledge the Wajarri Yamatji people as the traditional owners of the Observatory site.

**Design - PREPRODUCTION**

**COMMISSIONING**

**OPERATION**

#### **PRODUCTION**

**TESTS**

**COMMISSIONING**

OPERATION

- 1. Digital Receiver Cards Manufactured

- 2. Assembled and Tested

- 3. Shipped to Curtin / MRO

#### **PRODUCTION**

**TESTS**

**COMMISSIONING**

OPERATION

#### **DESIGNED FOR TESTABILITY**

### **Test coverage**

- 1) Physical

- 2) Power

- 3) Clock

- 4) Component level: FPGA, Fiber

- 5) Integrated tests

- 6) Digital system

- 7) Functional

- 8) Alignments

- 9) Start/stop

- 10) Power Cycle

- 11) Early Mortality: 15 days

- 12) Environmental

REPEATED MANY TIMES

# Firmware Diagnostic modes

Covering:

ADC

**Buffers**

Channelizer

Band pass monitoring

**Total Power monitoring**

Fiber data

Device up & up-time tests

**M&C** checksum

**PRODUCTION / TESTS**

**SHIPMENT**

**COMMISSIONING**

**OPERATION**

#### **PRODUCTION**

#### **TESTS**

#### **COMMISSIONING**

**OPERATION**

### Multiple Layers

- 1. Internal to Digital Receiver/SBC/DAS

- 2. ASC and Digital Receiver

- 3. Beamformers, ASC and Receiver

- 4. Tiles, Beamformers, ASC and Receiver

- 5. Source Scan autos, crosses

- 6. Between Receivers crosses

#### Assumes:

- a) Power b) Clock c) SCTN d) USB→SBC

- e) GbE → Computer/Laptop

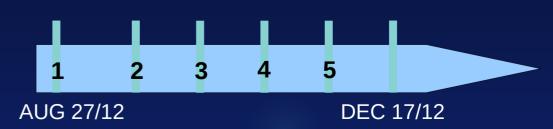

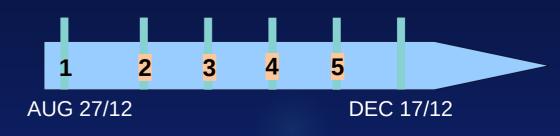

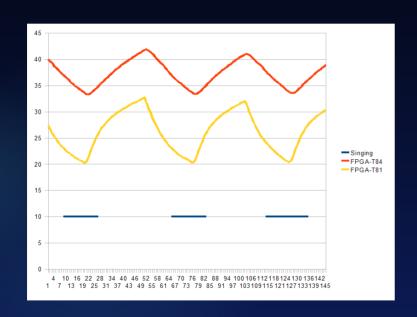

### plan

**128 tiles laid Tested in sub-arrays of 32 tiles**

### **Five sub-arrays:**

Alpha, Beta, Gamma, Delta and Epsilon

**Sub arrays overlapped with tested tiles**

**PRODUCTION**

**TESTS**

**COMMISSIONING**

OPERATION

Alpha receivers (32 tiles) commissioned with verification conducted from MRO site plan

128 tiles laid Tested in sub-arrays of 32 tiles

**Five sub-arrays:**

Alpha, Beta, Gamma, Delta and Epsilon

**Sub arrays overlapped with tested tiles**

**PRODUCTION**

**TESTS**

**COMMISSIONING**

**OPERATION**

plan

128 tiles laid Tested in sub-arrays of 32 tiles

**Five sub-arrays:**

Alpha, Beta, Gamma, Delta and Epsilon

Sub arrays overlapped with tested tiles

Remaining 96 tiles commissioned with receivers operated/checked from remote

**PRODUCTION**

**TESTS**

**COMMISSIONING**

OPERATION

128 tiles laid

Tested in subarrays of 32 tiles.

Five sub arrays:

Alpha, Beta, Gamma, Delta and Epsilon

Each sub array overlapped with tested tiles

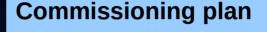

Temperature related issue

#### **Lessons learned**

#### COMMISSIONING

2<sup>7</sup> to 2<sup>17</sup>

- 1) FPGA design occupancy: 20 30% head room

- 2) Clocking: 10 % head room

- 3) Major Components: FPGAs and ADCs

- **4) Spare planning:** aligned with needed up time components 10% digitizer 5 % Storage

- 5) Lightning wind rain

- 6) Test for site conditions container inside container

- 7) Stress tests temperature cycle +/- 10 -20%

- 8) Power cycles

- 9) Cold & warm start tests

- 10) Board level tests clock/init

- **11) Integrated tests -** board level

- 12) IO interconnect tests

- 13) Monitoring and Control features

- 14) Low latency, fast & predictable response time